# Lógica Digital Combinacional

- Guía 6 -

**Laboratorio de Electrónica - Departamento de Física - FCEyN - UBA**

Cátedra: Schmiegelow

## Lógica Combinacional

1. Muestren que la compuerta OR-exclusiva (XOR) actúa como un inversor controlado: invierte la señal en una de sus entradas dependiendo del estado de la otra.

2. El integrado 74x86 agrupa cuatro compuertas XOR, mientras que los 74x00 conforman cuatro compuertas NAND.

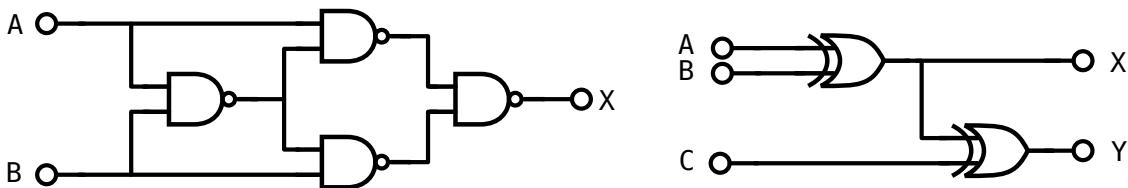

- a) Encontrar la tabla de funcionamiento de cada uno de los arreglos de compuertas de la siguiente figura. Construyan su tabla de verdad

- b) ¿Qué compuerta implementa el primer arreglo?

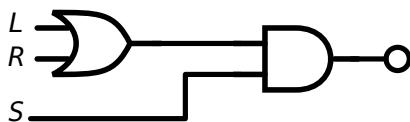

3. **Luces encendidas.** El siguiente circuito activa una alarma (BUZZ) cuando hay una luz del auto encendida (S) y se abre alguna de sus dos puertas (R,L).

- a) Construyan su tabla de verdad y comprueben que hace lo que uno espera.

- b) Extiendan el circuito para que solo se active si uno mueve la llave (K).

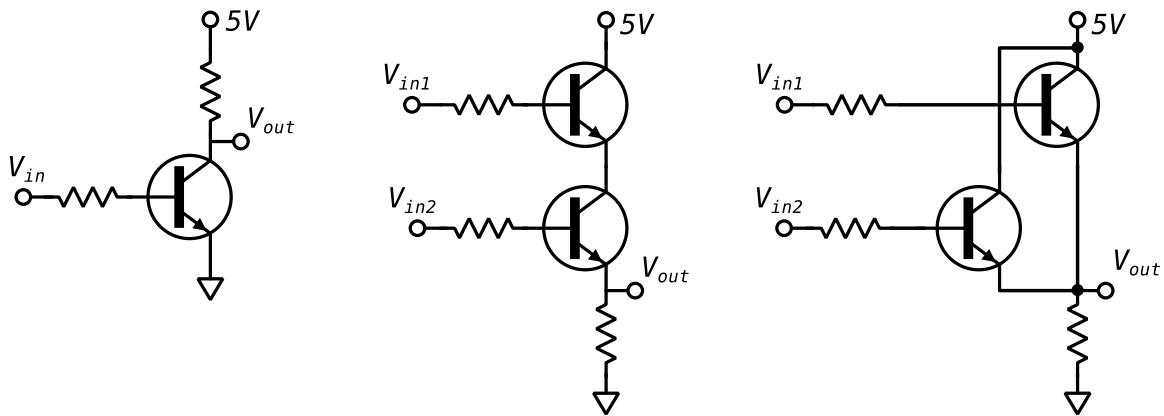

4. **Sumador.** El circuito de la siguiente figura se llama semisumador (“half adder”): suma dos bits dando el resultado y un bit de acarreo.

- a) Comprueben su funcionamiento armando su tabla de verdad.

- b) Dibujen, ignorando sus partes internas, un bloque que represente el semisumador.

- c) Construyan un sumador completo utilizando dos semisumadores. Un sumador completo toma tres entradas: a las señales a sumar permite sumarles una señal de acarreo.

- d) Dibujen, nuevamente ignorando sus partes internas, un bloque que represente el sumador completo.

- e) Utilizando cuatro sumadores completos, construyan un sumador de 4 bits.

**EXTRA** En general uno utiliza sumadores ya armados (integrados). Como por ejemplo el sumador de 4 bits SN7483. Hay, por ejemplo, contadores de 8 o de 16 bits. Busquen los números de componentes correspondientes.

5. **Clásicos Combinacionales.** Estudien qué hacen los siguientes tres circuitos lógicos integrados clásicos de la serie 7400.

- a) Multiplexor, ej 74x151

- b) Comparador , ej 74x85

- c) Driver de display de 7 segmentos, ej. 74x46

Bibliografía. Pueden encontrar una descripción de toda los integrados de la serie en:

[http://en.wikipedia.org/wiki/List\\_of\\_7400-series\\_integrated\\_circuits](http://en.wikipedia.org/wiki/List_of_7400-series_integrated_circuits)

6. Convirtan los siguientes números entre sistemas decimal, binario y hexagesimal según se indica.

- a) Convirtan a decimal: (i)  $1110101_2$  , (ii)  $11.01_2$  , (iii)  $4B_H$ .

- b) Convirtan a binario: (i)  $511_{10}$  , (ii)  $511_H$ . (iii)  $FF_H$

- c) Convirtan a hexagesimal: (i)  $1023_{10}$ , (ii)  $41243_{10}$ , (iii)  $101110101101_2$ .

**Extra** Los colores de un píxel en la PC se suelen representar como una terna conformada por el rojo (R), el verde (G) y el azul (B), donde cada uno puede tomar un valor entre 0 y 255. Siguiendo ese orden, escriban en notación hexagesimal los colores R, G y B puros. Esta notación permite nombrar únicamente y con 6 caracteres a los  $256^3 = 16777216$  posibles colores, donde los primeros dos corresponden al rojo, los siguientes dos al verde y los últimos al azul.

## Lógica con Transistores

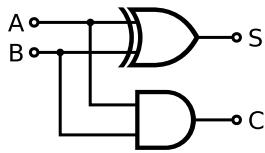

7. **Lógica Transistor-Resistor** Analizaremos una familia de circuitos lógicos llamada Resistor-Transistor Logic RTL. Una predecesora, un poco dejada de lado, de la popular TTL (transistor-transistor logic) que tuvo sus momentos de gloria en las primeras computadoras y en sistemas de control de misiones espaciales como las Apollo. Supongamos que deseamos codificar los símbolos binario {0,1} utilizando dos niveles de tensión: *bajo* (idealmente 0 V, aceptable hasta 0,8 V) y *alto* (idealmente 5 V, aceptable hasta 2 V). En la siguiente figura se muestran tres circuitos de una familia lógica más simple que realizan la operaciones lógicas elementales: negación (*NOT*), producto (*AND*) y suma (*OR*).

- a) Construyan una tabla con la tensión de salida esperada para cada combinación de las entradas e identifiquen cada una como nivel bajo o alto (tabla de verdad).

- b) Asignen valores a las resistencias para garantizar: (i) que los niveles de salida se encuentren en el rango adecuado en cada caso, (ii) que la impedancia de salida no supere los  $500\ \Omega$  y (iii) que la corriente de entrada sea  $< 1.5\ \text{mA}$ .

**Extra** Investiguen cómo son los circuitos equivalentes de las familias lógicas TTL y CMOS.

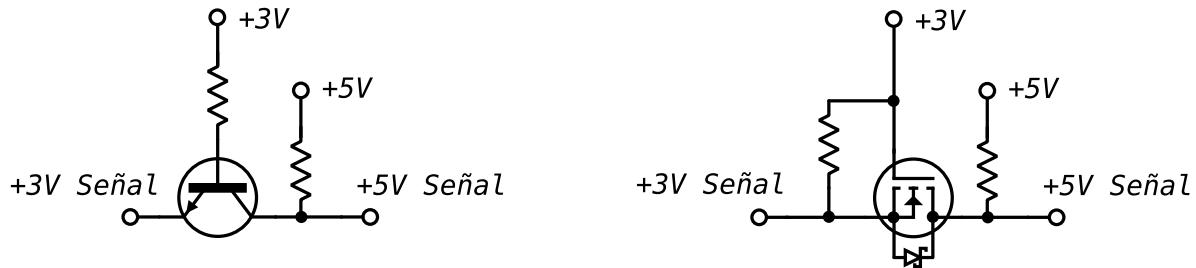

8. **Conversores de Tensión.** Es usual tener que convertir tensiones entre distintos sistemas lógicos. Por ejemplo entre un TTL de 0-5 V y un CMOS de 3.3 V. Existen varias topologías de circuitos para hacerlo. Estudien las siguientes dos topologías, utilizando transistores bipolares en un caso y MOSFETs en el otro y discutan su funcionamiento. Discutan si son uni-direccionales o bi-direccionales.

**Notas** Conversores MOSFET: nota de aplicación de Phillips AN97055. "Bi-directional level shifter for I2C-bus and other systems".

Conversores Bipolares: <https://electronics.stackexchange.com/questions/296879/logic-level-converter-using-transistors>

## Etapas de entrada y salida

9. **Estados indeterminados.** En una compuerta CMOS (por ejemplo, un inversor 74HC04), por error una de sus entradas queda desconectada (flotante). Medir la señal en la salida con un osciloscopio. Preguntas:

- ¿Qué se esperaría observar en la pantalla del osciloscopio? (un '0' limpio, un '1' limpio, o algo más?).

- Explicar por qué sucede esto a nivel físico (piensa en los transistores MOSFET de la entrada).

10. **Pull-up y down** ¿Qué valor de resistencia utilizaría en cada caso?

- Un pulsador normalmente abierto que debe generar un '1' lógico cuando es presionado y un '0' cuando no lo es, para una entrada TTL.

- Un pulsador normalmente abierto que debe generar un '0' lógico cuando es presionado y un '1' cuando no lo es, para una entrada CMOS.

c) La conexión entre la salida de un sensor (colector abierto) y una entrada CMOS.

11. **Compatibilidad ttl-cmos y cmos-ttl.** Analizar la compatibilidad de los niveles lógicos en las siguientes interfaces. Asume una alimentación de +5V para ambos circuitos.

a) Salida TTL (Serie 74LS) ->Entrada CMOS (Serie 74HC)

Un '0' TTL (0.4V máx.) es claramente un '0' para el CMOS (umbral 1.5V). ¿Qué problema potencial hay con el nivel '1' TTL (2.7V mín.) frente al umbral de '1' CMOS (3.5V mín.)? Proponer soluciones para este problema

b) Salida CMOS (Serie 74HC) ->Entrada TTL (Serie 74LS)

Un '1' CMOS (casi 5V) es claramente un '1' para el TTL (2.0V mín.). Un '0' CMOS (casi 0V) es claramente un '0' para el TTL (0.8V máx.). ¿Cuál es el problema en esta situación? (Pista: Piensa en la corriente que puede entregar/drenar la salida CMOS vs. la que necesita la entrada TTL).